¡Hola! Publico más ahora que en mis inicios...

Había una cosa en mi Power Mac G4 MDD Dual 1.42GHz que no me dejaba descansar tranquilo, y es que me da la sensación de que Apple los "limitó" a posta para que no ensombrecieran los recién salidos G5...

Hacía tiempo que me había fijado en un detalle de los chips de caché de muchos MDD por encima de 1GHz, y es que son chips que soportan velocidades hasta 300MHz.

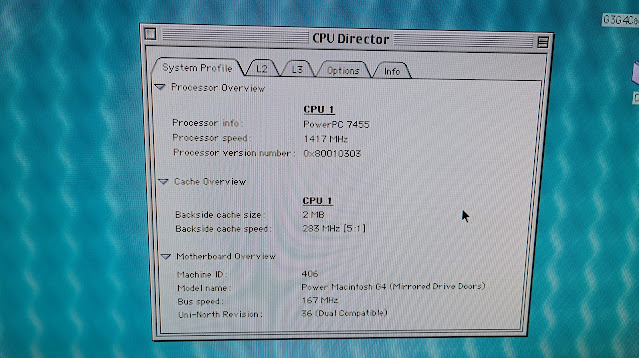

He estado buscando algún software que me permitiera verificar el ratio real de la caché y su velocidad, y gracias a este hilo de 68kmla, pude encontrar una versión de CPU Director que en un MDD y bajo OS9 me mostrara estos datos:

Increíble pero cierto, Apple fijó la velocidad de los chips de caché muy por debajo de su velocidad máxima. La velocidad de la caché se fija mediante una pequeña EEPROM que hay en las placas de procesador, igual que las localizadas en el iMac G3 tray que modifiqué.

Yo para estas cosas soy muy torpe, así que he intentado algo nuevo para mi, preguntar a una IA de confianza. Alguna vez había hecho consultas simples a GitHub Copilot, así que me propuse lanzarle un reto mayor: Que me ayude a modificar la EEPROM original para cambiar el ratio a 5:1.

Le he entregado los tres volcados originales, le he explicado qué ajustes tiene cada uno, y le he dicho que quizás haya un checksum al final sin el cual no funcione. En cuanto al ratio, ha sido muy rápido, resulta que cuando el ratio es 6:1 hay un 61 en la posición 0xA7, y cuando es ratio 4:1 hay en esa posición un 41. Así que debía cambiar el valor de 61 por 51. Para el checksum soy incapaz de explicaros cómo se calcula, sólo tuve que corregirle la posición del checksum, pues en lugar de en 0xAF lo colocaba en 0xAB, no interpretó que era una tabla de 16x16, pero una vez aclarado eso, me calculó el checksum. Debía cambiar en 0xAF el valor de DB por FD.

¡FUNCIONA! La caché L3 ha subido de 233MHz (6:1) a 283MHz (5:1). No creo que suponga ninguna barbaridad en rendimiento, pero así debió haber salido de fábrica.

No hay comentarios:

Publicar un comentario